1. 기능안전 기반 안전 메커니즘의 정의와 필요성

ISO 26262 기능안전 표준에서는 시스템이 안전 상태(Safe State)에 도달하거나 이를 유지할 수 있도록 고장을 감지하고 제어하는 기술적 장치나 기능을 안전 메커니즘(Safety Mechanism)이라고 정의합니다. 다시 말해, 시스템 내 단일 고장(single point failure)이나 잠재 고장(latent failure)을 사전에 방지하거나 발생 시 효과적으로 대응하여, 운전자에게 고장 정보를 제공하거나 시스템을 안전 상태로 전환해주는 역할을 수행합니다.

또한 차량 시스템에는 개발 과정에서 발생하는 Systematic Fault(체계적 고장)과 운용 중 물리적으로 발생하는 Random Fault(무작위 고장) 두 가지 유형의 고장이 존재하며, 이들은 각각 사전에 제거하거나 운전 중 실시간으로 대응해야 할 대상입니다. 따라서, 모든 고장 시나리오에 대해 효과적으로 대응하고 안전 목표를 달성하기 위해서는, 적절한 안전 메커니즘이 반드시 설계에 포함되어야 합니다.

첫째, 체계적 고장(Systematic Faults)은 설계, 제조, 또는 프로세스상의 오류로 인해 발생하며, 일반적으로 재현 가능하고 예측 가능한 특성을 가집니다. 시스템 및 소프트웨어에서 발생하는 고장은 본질적으로 체계적 고장으로 간주되며, 체계적 고장을 완화하기 위해서는 개발 과정에서 엄격한 프로세스 준수, 설계의 이중화 또는 진단 로직, 철저한 검증/확인 활동, 그리고 MISRA C와 같은 코딩 표준의 적용이 요구됩니다.

둘째, 무작위 하드웨어 고장(Random Hardware Faults)은 부품 노화, 물리적 결함, 또는 SEU(Single-Event Upsets)* 와 같은 예측 불가능한 사건들에 의해 발생합니다. 이러한 고장의 발생률 자체를 줄일 수는 없으므로, 핵심 전략은 안전 메커니즘(SM)을 설계에 통합하여 고장을 실시간으로 감지하고 처리함으로써 애플리케이션의 실패를 방지하는 것입니다. 특히 높은 ASIL 목표(C 또는 D)를 달성하기 위해서는 고장 발생 후에도 기능을 유지할 수 있는 높은 수준의 고장 내성(Fault Tolerance)이 요구되며, 이는 안전 메커니즘의 핵심 목표가 됩니다.

* SEU (Single-Event Upset) : 우주 방사선이나 고에너지 입자(예: 중성자, 이온 등)가 반도체 소자 내부에 충돌하면서, 메모리 셀이나 레지스터의 비트 값이 순간적으로 뒤바뀌는 현상(0↔1)

이러한 안전 메커니즘은 차량 개발 시 시스템, 하드웨어, 소프트웨어 각 단계에서 안전 목표(ASIL 등급)를 만족하기 위해 반드시 고려해야 하는 핵심 요소 중 하나입니다. 결국 잠재적인 위험을 체계적으로 식별·완화하고 안전 목표를 달성하기 위해, 고장 검출과 완화 수단으로서 다양한 안전 메커니즘이 필요합니다.

여기서는 시스템 및 하드웨어, 소프트웨어 레벨에 필요한 대표적인 안전 메커니즘(Safety Mechanism)을 기술하고자 합니다.

2. 안전 메커니즘(Safety Mechanism, SM)의 정의 및 역할

안전 메커니즘(Safety Mechanism, SM)의 정의는 시스템이 안전 상태(Safe State)에 도달하거나 이를 유지할 수 있도록 고장을 감지하고 제어하는 기술적 방안이나 기능을 의미합니다. SM은 시스템 내 단일점 고장(SPF: Single Point Fault)이나 잠재 고장(LF: Latent Fault)을 사전에 방지하거나, 고장 발생 시 효과적으로 대응하여 위험을 완화하는 역할을 수행해야 합니다. 아래 내용은 고장에 안전 메커니즘의 효율성과 관련된 고장의 종류 입니다.

단일점 고장 (SPF, Single-Point Fault): 안전 메커니즘(SM)에 의해 전혀 커버되지 않아 고장 발생 즉시 안전 목표 위반으로 이어지는 고장으로, SM 설계의 최우선 목적은 시스템 내에 이러한 SPF가 남지 않도록 모든 잠재적 고장 경로를 감지하고 완화하는 것입니다.

잠재 다중점 고장 (LMPF, Latent Multiple-Point Fault): 안전 메커니즘에 의해 검출되지 않거나 운전자에 의해 인지되지 않고 잔존하다가, 다른 독립적인 고장과 결합하여 안전 목표 위반으로 이어지는 고장입니다. SM, 특히 주기적인 진단 기능은 이러한 잠재 고장을 정해진 시간 내에 감지하여 위험 노출 시간을 최소화하는 역할을 수행합니다

잔여 고장 (RF, Residual Fault): SM이 부분적으로만 고장을 제어하여, 고장 모드의 일부가 여전히 안전 목표 위반으로 이어질 수 있는 경우이며, 이는 SM의 진단 범위(DC)가 100% 미만일 때 발생하는 필연적인 부분으로, 높은 ASIL 시스템에서는 DC를 최대화하여 잔여 고장의 발생률을 극도로 낮추어야 합니다.

SM의 주요 기능은 이러한 고장 검출(Fault Detection)과 고장 완화(Mitigation)이며, 단순히 고장을 감지하는 것을 넘어, 고장이 안전 목표 위반으로 이어지는 것을 방지하거나 시스템을 안전한 상태로 전환하는 역할을 수행합니다. SM의 효율성은 진단 범위(Diagnostic Coverage, DC)라는 계수로 측정하며, DC는 해당 SM이 감지하고 처리할 수 있는 고장의 비율을 나타내며, 이는 0%에서 100% 사이의 값으로 도출하고, 이러한 DC를 확보하는 것은 ISO 26262의 하드웨어 안전 지표(Hardware Metrics) 달성에 필수적입니다.

3. 안전 메커니즘의 분류 및 사례

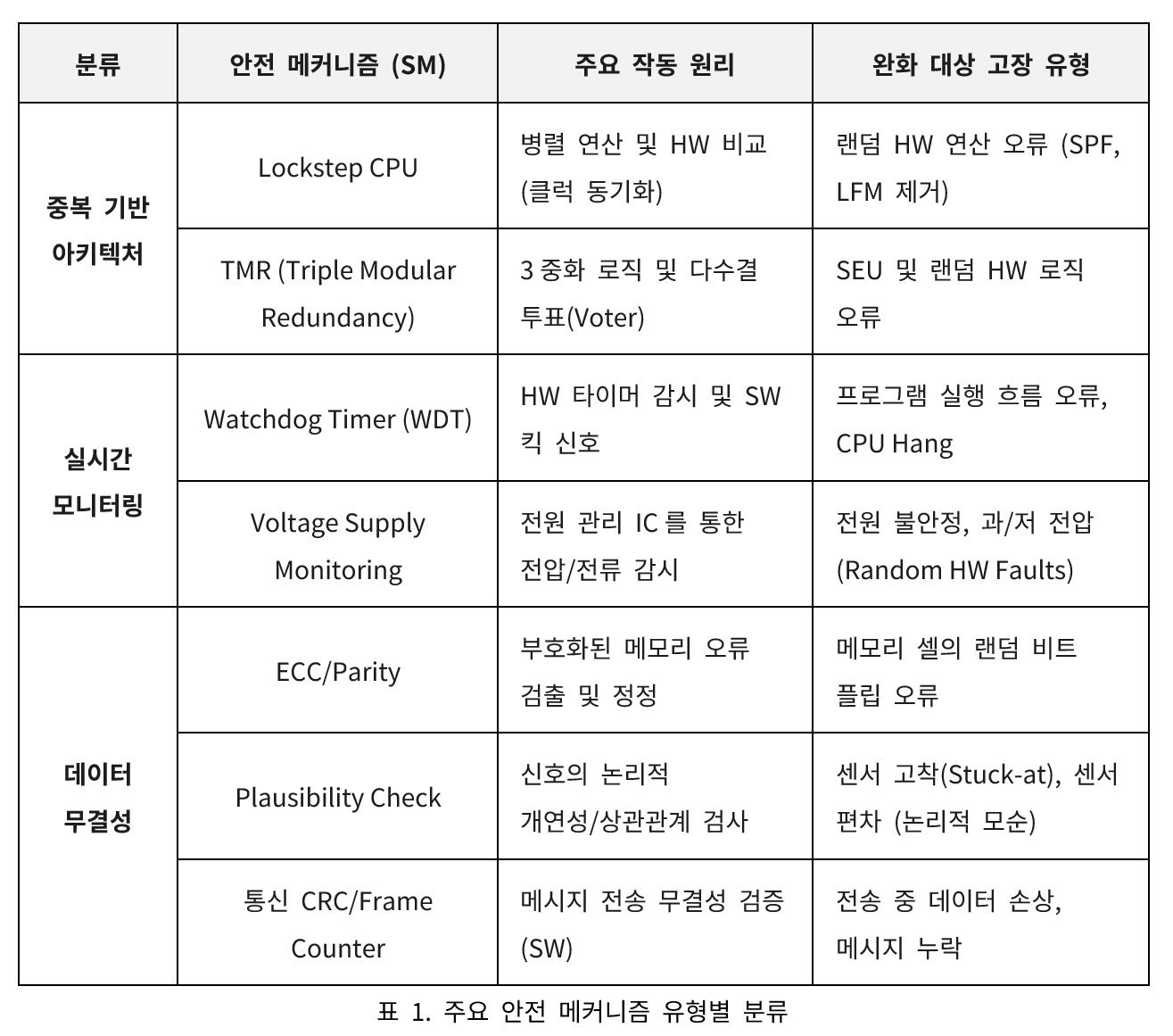

Safety Mechanism Handbook(내부 분류 자료)를 기반으로 다양한 안전 메커니즘들을 그 작동 범위와 구현 방식에 따라 다음과 같이 세 가지 범주로 분류할 수 있습니다. 첫째 높은 ASIL 등급(ASIL C, AISL D)의 안전목표를 달성하기 위해 중복기반 아키텍처가 요구되며, 둘째 일반적으로 ASIL A 및 B와 같은 ASIL 시스템은 고장을 감지(Detect)한 후 시스템을 안전한 상태로 전환하거나 더 높은 ASIL 시스템에 해당 고장을 알려주어야 합니다. 마지막으로 이러한 부분을 모두 가능하게 하는 방법 중 하나가 안전기능에 사용되는 데이터이 검증입니다. 이러한 요구사항을 만족하기 위해 일반적으로 세 가지의 안전 메커니즘으로 분류가 가능합니다.

카테고리 I: 중복기반 아키텍처 관련 SM

카테고리 II: 실시간 모니터링/진단 관련 SM

카테고리 III: 데이터 무결성/논리성 검증 관련 SM

아래에서는 각 범주별로 주요 안전 메커니즘 사례를 들고, 그 개념과 작동 원리를 실무 관점에서 간단히 요약합니다.

4. 주요 안전 메커니즘 상세 분석 및 실무 사례

4.1. 카테고리 I: 중복 기반 아키텍처 (Redundancy-Based Mechanisms)

이 메커니즘들은 물리적 혹은 논리적 중복 구조를 활용하여 단일 고장 발생 시에도 시스템의 기능 연속성을 보장하거나 고장을 정정함으로써 높은 고장 내성(Fault Tolerance)을 실현합니다. 이는 특히 ASIL D와 같이 엄격한 안전 요구사항을 충족하는 데 필수적입니다.

멀티 코어 락스텝 (Lockstep CPU): 마이크로컨트롤러 내부에 두 개 이상의 프로세서 코어를 배치하여 동일한 연산을 클럭 단위로 동시에 수행하게 하고, 그 결과를 하드웨어 비교기(Comparator)를 통해 실시간으로 상호 비교하는 구조입니다. 이 방식은 CPU 내부 연산에서 발생하는 미세한 오류나 무작위 고장을 즉시 감지하고, 해당 오류가 시스템 전체에 전파되는 것을 방지함으로써, 높은 ASIL MCU에서 CPU 연산 무결성을 보장하는 가장 효과적인 수단으로 널리 사용됩니다.

TMR (Triple Modular Redundancy) 및 다중화: TMR은 세 개의 동일한 모듈(로직, 메모리, 또는 센서 채널)을 중복하여 구성하고, 이들의 출력단에 다수결 투표 회로(Majority Voter)를 두는 방식입니다. 세 모듈 중 하나의 모듈에 고장이 발생하여 잘못된 값이 나오더라도, 회로가 나머지 두 모듈의 일치하는 값을 선택하여 고장을 자동으로 교정(Correction)하고 기능 손실 없이 동작을 지속합니다. 이는 특히 안전에 치명적(Safety critical)인 시스템과 같은 차량용 메모리/로직에서 발생하는 소프트 에러(SEU)에 대한 고장 내성을 제공하며, ASIL D 요구사항 충족에 핵심적인 역할을 합니다.

이중/다중 채널 신호 비교: 중요한 센서나 액추에이터 구동 신호를 이중화 하거나 다중화하여 출력 신호를 실시간으로 비교함으로써 고장을 감지하는 방법입니다. 예를 들어, 듀얼 센서 출력값을 하드웨어 비교기를 통해 대조할 경우, 한 채널의 오류는 즉시 불일치로 검출되어 최종 제어 단계로 잘못된 값이 전달되는 것을 막을 수 있습니다.

통신 버스의 하드웨어 중복: CAN이나 FlexRay와 같은 차량 네트워크에서 물리적인 배선을 이중화(Complete Redundancy)하여 한쪽 선로에 단선이나 합선 등의 물리적 고장이 발생하더라도 나머지 통신망을 통해 기능 수행을 지속할 수 있으며, 이는 Fail-Operational 시스템에서 통신 무결성과 가용성(Availability)을 높이는 데 필수적입니다.

4.2 카테고리 II. 실시간 모니터링 및 진단 (Runtime Monitoring & Diagnostics)

이 메커니즘들은 시스템의 운영 상태, 실행 흐름, 물리적 조건을 감시하여 시스템 전체의 이상 징후를 조기에 감지하고 안전 상태로의 전환(Fail-Safe)을 유도하는 데 중점을 둡니다.

Watchdog Timer (WDT): MCU의 동작을 감시하는 하드웨어 타이머로, 소프트웨어가 정해진 주기 내에 정상 신호(Heartbeat 또는 Kick)를 보내지 않으면 시스템에 이상이 발생한 것으로 판단하여, 소프트웨어 실행이 정지되거나 무한 루프에 빠지는 오류를 감지하면 시스템을 자동으로 리셋 하거나 오류 처리 절차를 실행하여 위험한 상태를 방지합니다. 정교한 WDT는 너무 느리거나 빠른 주기의 신호까지도 오류로 간주하여 프로그램 흐름 이상을 정밀하게 감지합니다.

Program flow and timing monitoring: 소프트웨어 내부에 설정된 루틴 실행 순서나 주기가 올바 른지 감시하는 기법입니다. 예를 들어 시간 기반 모니터(타임아웃)와 논리 흐름 모니터를 조합하여 프로그램이 지정된 시간 안에 특정 작업을 완료하는지, 그리고 함수 호출 순서 등이 어긋나지 않았는지 확인합니다. 일정 시간 내 완료되지 않거나 수행 순서가 어긋나면 소프트웨어는 이를 오류로 인지하고 안전 모드로 전환하거나 시스템을 재 시작합니다. (예시: 윈도우 워치독은 너무 빠르거나 늦은 주기의 신호도 오류로 간주하여, 프로그램 흐름 이상을 정교하게 잡아냅니다.

Voltage Supply Monitoring: 시스템에 인가되는 전압 또는 전류를 하드웨어적으로 감시하여 기준 범위를 벗어날 경우 경고를 주거나 시스템을 종료합니다. 예를 들어 과 전압이나 저 전압이 감지되면 ECU를 리셋 하거나 안전 모드로 전환하여 전체 시스템의 손상을 막습니다. 이러한 전원 모니터링 IC/회로는 시스템 전반의 전원 안정성을 보장함으로써 차량 전장품의 오동작을 예방합니다.

4.3 카테고리 III. 데이터 무결성 및 논리 검증 (Data Integrity & Plausibility Checks)

이 메커니즘들은 데이터의 저장, 연산, 또는 통신 과정에서 발생하는 오류를 검출하고 정정하여, 잘못된 데이터가 제어 결정에 사용되는 것을 방지함으로써 시스템의 신뢰성을 확보 합니다.

ECC (Error Correction Code) 및 Parity: 메모리 영역에서 발생하는 무작위 비트 뒤바뀜 오류를 처리하기 위해 사용되며, ECC 메모리는 데이터 워드와 함께 검사 코드를 저장하여 1비트 오류는 자동으로 교정(Correction)하고 다중 비트 오류는 검출합니다. 패리티 검사는 가장 단순한 형태로, 각 데이터에 홀수/짝수 패리티 비트를 추가하여 읽을 때 오류를 감지하는 방식이며, 이러한 기법은 메모리에서 발생하는 무작위 고장을 즉시 발견하여 데이터 신뢰성을 크게 향상시킬 수 있습니다.

Checksum/CRC (Cyclic Redundancy Check): 통신 메시지나 메모리 데이터의 무결성을 소프트웨어적으로 확인하는 방법으로 송신 측에서 계산된 CRC 값을 메시지와 함께 전송하고, 수신 측에서 동일한 알고리즘으로 재계산한 값과 비교하여 전송 중 발생한 비트 오류를 검출합니다. 이러한 정보 기반 무결성 검사는 구현이 비교적 간단하면서도 데이터 손상으로 인한 위험을 효과적으로 완화합니다.

논리상 개연성 검사 (Plausibility Check): 센서 신호나 상태 값이 물리적 및 논리적으로 타당한지 판단하는 기법이다. 예를 들어, 입력값이 유효 범위(Valid Range)를 벗어나거나, 복수의 센서 신호가 서로 상관관계 검사(Correlation Check)를 통해 모순되는 경우, 해당 신호를 오류로 식별하고 안전 모드로 전환하거나 경고를 활성화합니다. 이 메커니즘은 소프트웨어 알고리즘으로 구현되지만, 센서의 고착(Stuck-at) 고장처럼 하드웨어 진단이 놓치기 쉬운 이상을 초기에 발견하는 데 매우 중요한 역할을 수행합니다.

5. 결론 및 제언

본 문서는 ISO 26262 기반의 안전 메커니즘(SM)이 시스템의 안전 목표 달성에 필수적인 항목으로, 1)중복 기반 아키텍처, 2)실시간 모니터링/진단, 3)데이터 무결성/논리 검증의 세 가지 핵심 기능 안전 원리로 구분합니다.

이 기능적 분류는 설계자가 요구되는 ASIL 수준에 따라 SM을 전략적으로 선택하는데 도움을 제공할 수 있습니다. ASIL A, B와 같은 레벨에서는 주로 모니터링 및 진단(카테고리 II/III)을 통한 고장 감지 후 안전 상태로의 전환(Fail-Safe)이 일반적입니다. 그러나 ASIL C, D와 같은 높은 레벨에서는 Lockstep CPU, TMR, ECC와 같은 중복 기반 아키텍처 및 진단(카테고리 I/III)을 통해 고장 교정(Correction)능력과 고장 내성(Fault Tolerance)을 확보하는 것이 필수적입니다. 이러한 고장 교정 능력은 잔여 고장(RF)의 비율을 최소화하고, ASIL C, D의 엄격한 하드웨어 지표를 충족시키는 근본적인 수단이 될 수 있습니다.

위에서 설명한 내용은 다양한 차량 안전 메커니즘을 실무 관점에서 참고할 수 있는 분류 기준 기준입니다. 실제 프로젝트에서는 아이템 레벨의 HARA, 시스템 아키텍처 구조, 기능 안전 목표(ASIL), 위험 분석(FMEA/FTA/DFA/ETA/FMEDA) 결과 등에 따라 개별 안전 메커니즘의 적용 여부나 구현 방식이 달라질 수 있습니다.